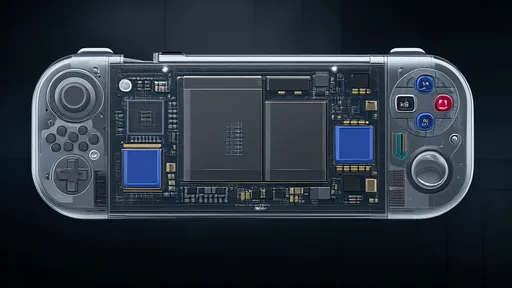

The evolution of data transfer speeds has taken another monumental leap with the introduction of PCIe 6.0. As the latest iteration of the Peripheral Component Interconnect Express standard, PCIe 6.0 promises to revolutionize how data moves between components in high-performance computing systems. With a staggering bandwidth of 64 GT/s (gigatransfers per second) per lane, this new standard effectively doubles the throughput of its predecessor, PCIe 5.0. The implications for data centers, artificial intelligence applications, and high-speed networking are profound, as the demand for faster and more efficient data transfer continues to grow exponentially.

The architecture behind PCIe 6.0 represents a significant departure from previous generations. One of the most notable advancements is the adoption of PAM-4 (Pulse Amplitude Modulation with 4 levels) signaling, a technology borrowed from high-speed networking. Unlike the traditional NRZ (Non-Return to Zero) encoding used in earlier PCIe versions, PAM-4 allows for two bits of data to be transmitted per clock cycle, effectively doubling the data rate without increasing the frequency. This innovation comes with its own set of challenges, particularly in terms of signal integrity, but the PCI-SIG (PCI Special Interest Group) has implemented robust error correction mechanisms to maintain reliability.

Latency reduction is another critical improvement in PCIe 6.0. While raw bandwidth often grabs headlines, the subtle enhancements in latency can make a substantial difference in real-world performance. The new standard introduces FLIT (Flow Control Unit) mode, which replaces the traditional packet-based data transfer with a more efficient flit-based approach. This change not only reduces overhead but also improves power efficiency, a crucial factor in large-scale deployments where energy consumption directly impacts operational costs. The combination of higher bandwidth and lower latency opens up new possibilities for memory-intensive applications such as machine learning training and real-time analytics.

The impact of PCIe 6.0 on data center infrastructure cannot be overstated. Modern data centers are grappling with the challenges posed by hyperscale computing and the proliferation of accelerators like GPUs and TPUs. These components require massive amounts of data to be shuttled between memory, storage, and processing units at unprecedented speeds. PCIe 6.0 addresses this need by providing the necessary bandwidth to prevent bottlenecks in these data flows. Furthermore, the backward compatibility of the standard ensures a smooth transition path for existing infrastructure, allowing data center operators to upgrade their systems incrementally without requiring complete overhauls.

Artificial intelligence and high-performance computing stand to benefit immensely from PCIe 6.0's capabilities. AI workloads, particularly those involving large language models or complex neural networks, are notoriously data-hungry. The faster interconnect speeds enable more efficient distribution of workloads across multiple accelerators, reducing training times and improving overall system utilization. In scientific computing applications, where simulations may involve petabytes of data, the reduced latency and increased throughput can significantly accelerate time-to-solution for complex problems. These advancements come at a critical time as the industry pushes the boundaries of what's possible in machine learning and computational research.

The adoption curve for PCIe 6.0 is expected to follow a similar pattern to previous generations, with enterprise and cloud providers leading the way. While consumer applications may not immediately require the full bandwidth offered by PCIe 6.0, the technology will eventually trickle down to mainstream devices as applications evolve to take advantage of the increased capabilities. Storage solutions, in particular, are poised for a transformation, with next-generation NVMe drives expected to saturate PCIe 6.0 lanes, delivering unprecedented storage performance that could redefine how we think about system architecture and data access patterns.

Thermal and power considerations present ongoing challenges for PCIe 6.0 implementation. The increased data rates generate more heat, requiring sophisticated cooling solutions, especially in dense server configurations. However, the standard incorporates several power efficiency improvements, including enhanced low-power states and more granular power management capabilities. These features help mitigate the thermal impact while maintaining performance, ensuring that the benefits of the higher speeds aren't offset by excessive power consumption or cooling requirements. System designers will need to carefully balance these factors when implementing PCIe 6.0 in their products.

The future of interconnect technology continues to evolve rapidly, with PCI-SIG already working on specifications for PCIe 7.0. However, PCIe 6.0 represents a significant milestone that will likely dominate the market for several years. Its combination of raw speed, improved efficiency, and backward compatibility makes it a versatile solution for a wide range of applications. As the industry begins to deploy systems leveraging this new standard, we can expect to see innovative uses that push the boundaries of computing performance, enabling breakthroughs in areas ranging from scientific research to consumer applications that we can only begin to imagine today.

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025